THE best way to find a PCB fabricator, anywhere.

### Speedy Circuits Co., Ltd.

Chung Li, Taoyuan, Taiwan

where quickturn & small volume PCB orders are all done in-house

Overview

Contact

Specs

About

Videos

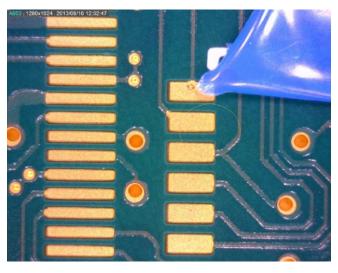

**Photos**

**Brochures**

News

We own & operate an ISO & UL manufacturing firm with complete in-house fabricating services facility that fulfills the requirements of tech customers worldwide for quick turnaround PCB prototypes as well as small-volume orders, complex HDI-SBUs, & IC substrates.

### Our Advantages:

- 1) Quick response, quote, service, & solutions.

- 2) A 400-strong workforce, including 60+ dedicated engineers, working round the clock manning 36 PCB processing stations to offer quick 1 to 5-day turnaround times.

Markets: Automotive, Communication, Computers,

Consumer, Industrial, Other: Biometrics, Robotics,

Internet of Things

**Board Types:** Single-sided, Double-sided, Millayer, Flex,

Rigid-Flex, Other: HDI SBU, IC s strates PTSE

Teflon, Thick Board Pro Cards, N

Heavy Copper.

rototype, Small, Medium

sembly, Quick turn-around

nd/buried vias, Carbon contacts, Con oth drilling, Controlled Impedance, Hoper, HDI, Sequential lamination

ISO 9001, ROHS compliant, UL

Featured Showcase

Click here to see a demo

### Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- Quick and easy "Contact" and "RFQ" buttons

- News, web and contact links

Click to see a partial list of registered OEMs!

www.thepcblist.com

# ADVANCEMENTS IN THERMAL MANAGEMENT 2015

AUGUST 5-6, 2015 • DENVER, CO.

### 2015 CONFERENCE PRELIMINARY PROGRAM ANNOUNCED

The Advancements in Thermal Management 2015 conference has released its preliminary program. A great lineup of speakers has been confirmed, with more speakers and official times to be announced in April.

2015 speaking companies include: IBM Research, Honeywell Electronic Materials, Cradle North America, University of Leeds, FLIR, United Arab Emirates University, Heraeus Electronic Materials, Outlast Technologies and many more.

### Preliminary Program Sessions Include:

- Thermal-Packaging Landscape: From Back-Side to Volumetric Heat Removal IBM Research

- Meeting the Thermal Management Needs of Evolving Electronics Applications

Honeywell Electronic Materials

- Co-Design by Electric and Mechanical Designers Using Real Time Thermal Analysis System

Cradle North America

- Phase-Change Heat Transfer at Micro/Nanoscale: from Fundamentals to Manufacturable Devices - University of Colorado

- Stand-Alone Packaged Thermal Sensors Based on Thermoelectric Effect LITEN/CEAN

- Thick Film Solutions to HOT Problems in Electronics Heraeus Electronic Materials

- Ceramic Thermal Management CeramTec GmbH

- Thermal Management of Electronic Devices Utilizing Latent Heat Sink (LHS) Materials

Outlast Technologies

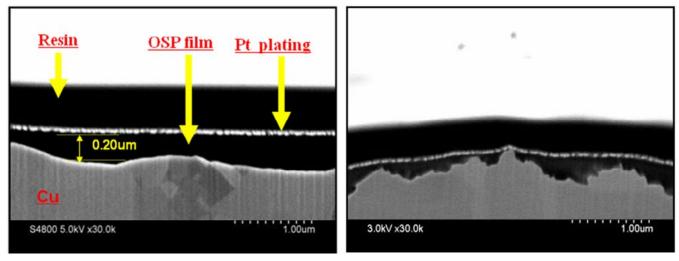

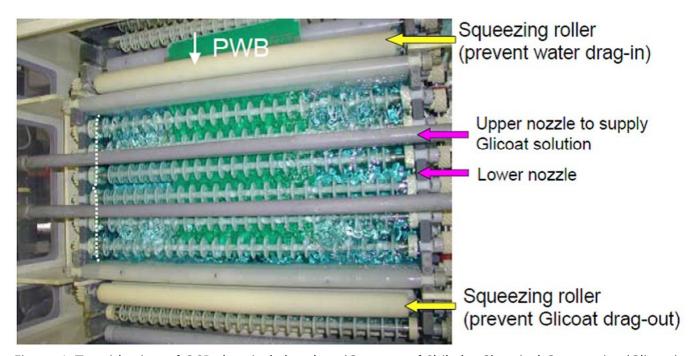

- Developments in Advanced Working Fluids for Phase Change Heat Transfer Devices

Flux Thermal Solutions

- Two-Phase Thermal Management for Next Generation High Power Systems i2C Solutions,

- Evaluation of PCMs Integrated into Heat Sinks for Enhanced Cooling in Electronic Packaging - United Arab Emirates University

- The Truth about the Accuracy of Measuring Temperature with Infrared Cameras FLIR Systems

- PCM Based Energy Storage Materials and Thermal Management Applications Phase Change Materials

- Thermal Performance of Fully Immersed Server into Saturated Fluid Porous Media University of Leeds

Interested in Exhibiting? Contact Will Massey at;

WilliamsM@WebcomCommunications or 800-803-9488 x.125

www.ThermalNews.com/Conferences

### **April Featured Content**

This month, **high density interconnect** gets the scrutiny of industrial professionals from TTM Technologies, Multek, and Gardien Services, who discuss the challenges of ultra-thin HDI PCB manufacturing, and how HDI relates to the Internet of Things (IoT) and substrate test fixtures.

## 8 Next-Generation Ultra-Thin HDI PCB Manufacturing Challenges

by Tarja Rapala-Virtanen, Erkko Helminen and Timo Jokela

### 20 High-Density Interconnects: Enabling the Intelligence of Things

by William Beckenbaugh, Ph.D. and Joan K. Vrtis, Ph.D.

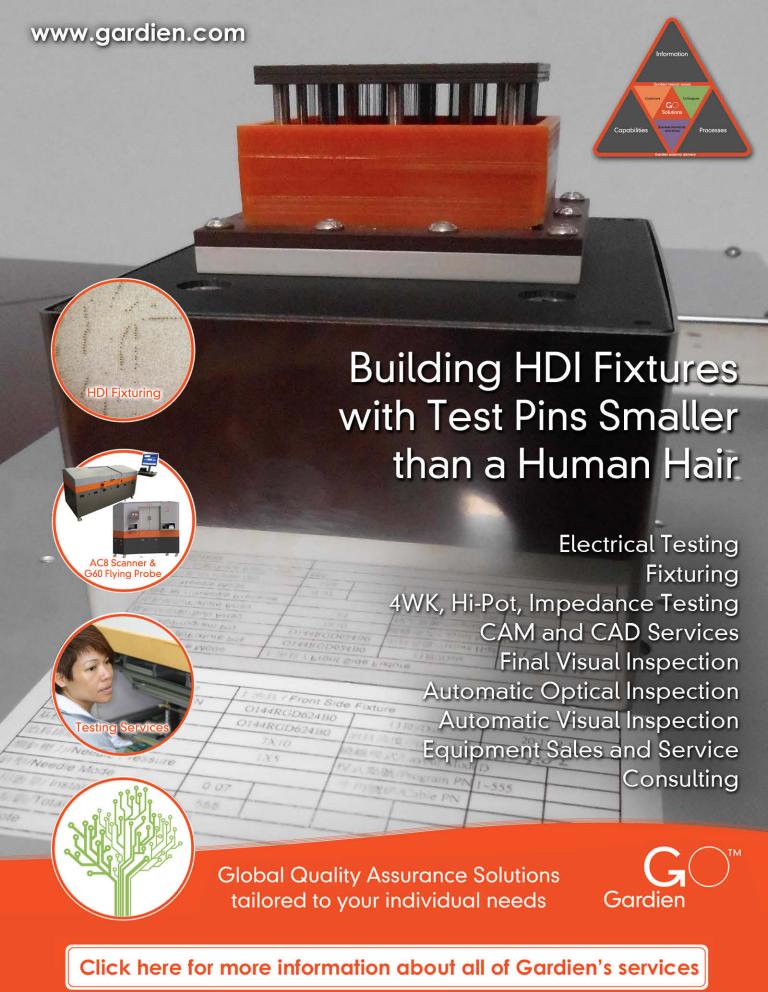

# 32 Splitting Hairs: The Manufacture of HDI and Substrate Test Fixtures by Todd Kolmodin

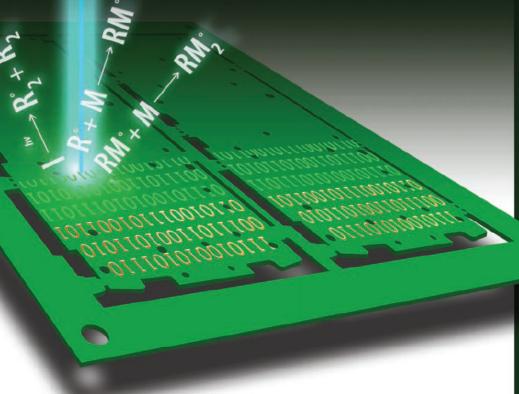

# DIRECT SOLDER MASK & LEGEND DEPOSITION BY INKJET TECHNOLOGY

**One-Stop-Shop for Solder Mask and Legend Deposition**

- Enhanced performance

- Short cycle time

- Reduced cost

- Green technology

For live demo in Southern California or for more details please feel free to contact: Gryphon-Demo@Camtek.co.il

**APRIL 2015 VOLUME 5**

**NUMBER 4**

THE DEFINITIVE **INTERACTIVE MAGAZINE DEDICATED TO THE GLOBAL PCB INDUSTRY**

magazine

CONTENTS

thepcbmagazine.com

an I-Connect007 publication

### **INTERVIEW**

42 The Challenges of the Fast-Moving **Wearables Market**

**COLUMNS**

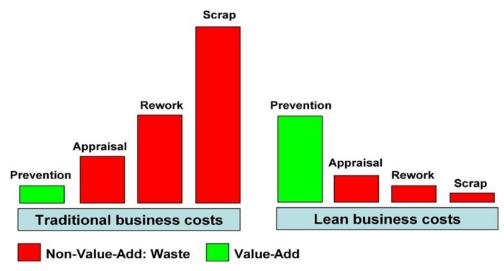

48 Best Practices 101: Part 6 by Steve Williams

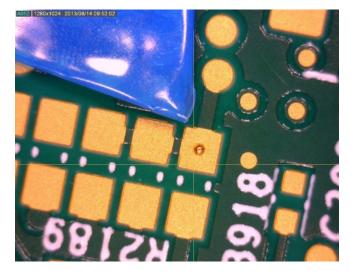

54 Copper Discoloration and Other Concerns with OSP by Michael Carano

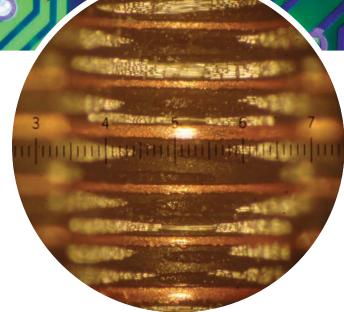

**62** Electrical Test: Surface Finish vs. Water Marks by Todd Kolmodin

**68** Design Considerations: Flexible Circuit vs. **Traditional PCB** by John Talbot

**NEWS HIGHLIGHTS**

- 40 Market

- **52** Supplier/New Product

- 60 Mil/Aero007

- 74 Top Ten PCB007 Highlights

### **VIDEO INTERVIEWS**

58 Inkjet Solder Mask Becomes a Practical Reality

66 John Davignon Discusses HDPUG

### **SHORTS**

- 46 Fascinating Quantum Transport on a Surface

- 72 Smart Factory 1.0: the Future of **Electronics** Manufacturing

### **EXTRAS**

**76** Events Calendar

77 Advertisers Index & Masthead

# Low-loss Laminate Materials for RF/Microwave/Millimeter-wave Designs

For over 100 years, Isola has been driving technology forward while improving end-product design with topperforming laminate and prepregs.

Our legacy continues with global R&D pushing our product line to the forefront in demanding RF/microwave designs.

With 10 manufacturing sites around the world, global quickturn capability, world-class technical service, measurement & modeling capabilities, and industry leading material development capabilities - Isola is well positioned to be your preferred RF/microwave partner.

The newest members of Isola's growing RF/Microwave laminate family now includes Terra Green™. a halogen-free, very low-loss, thermoset material that is available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

Astra®MT is a revolutionary ultra low-loss thermoset laminate replacement for PTFE, suitable for automotive radar, mm-wave and AESA applications.

I-Tera MT is available in core thicknesses from 0.002" to 0.018" and offers 18 different prepregs for optimal design flexibility.

I-Tera®MT RF is available in 20 and 30 mil cores and a 3.38 and 3.45 Dk.

|                                                                                                                                                                                                                                              | TerraGreen™     | Astra® MT       | I-Tera® MT/<br>I-Tera MT RF | IS680                                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------------------|------------------------------------------|--|

| Tg                                                                                                                                                                                                                                           | 200°C           | 200°C           | 200°C                       | 200°C                                    |  |

| Td                                                                                                                                                                                                                                           | 390°C           | 360°C           | 360°C                       | 360°C                                    |  |

| DK @ 10 GHz                                                                                                                                                                                                                                  | 3.45            | 3.00            | 3.45                        | 2.80 - 3.45                              |  |

| Df @ 10 GHz                                                                                                                                                                                                                                  | 0.0030          | 0.0017          | 0.0031                      | 0.0028 - 0.0036                          |  |

| CTE Z-axis (50 to 260°C)                                                                                                                                                                                                                     | 2.90%           | 2.90%           | 2.80%                       | 2.90%                                    |  |

| T-260 & T-288                                                                                                                                                                                                                                | >60             | >60             | >60                         | >60                                      |  |

| Halogen free                                                                                                                                                                                                                                 | Yes             | No              | No                          | No                                       |  |

| VLP-2 (2 micron Rz copper)                                                                                                                                                                                                                   | Standard        | Standard        | Available                   | Available                                |  |

| Stable Dk and Df over the temperature range                                                                                                                                                                                                  | -55°C to +125°C | -40°C to +140°C | -55°C to +125°C             | -55°C to +125°C                          |  |

| Optimized Global constructions for Pb-Free<br>Assembly                                                                                                                                                                                       | Yes             | Yes             | Yes                         | Yes                                      |  |

| Compatible with other Isola products for<br>hybrid designs                                                                                                                                                                                   | Yes             | Yes             | Yes                         | For use in double-<br>sided applications |  |

| Low PIM < -155 dBc                                                                                                                                                                                                                           | Yes             | Yes             | Yes                         | Yes                                      |  |

| NOTE: DK Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions |                 |                 |                             |                                          |  |

of the agreement under which they are sold.

### FREE WEBINAR

### PCB Material Selection for RF/Microwave/Millimeter-wave Design

This webinar will educate you on how to select the appropriate PCB material for RF, microwave and millimeterwave applications through careful consideration of cost constraints and system-performance parameters, such as the frequency of operation and bandwidth, the electrical size of board and its critical features, loss and uniformity requirements, temperature range of system operation, and thermal and processing considerations.

## by Tarja Rapala-Virtanen, Erkko Helminen and Timo Jokela

TTM TECHNOLOGIES INC.

### **Abstract**

High-density interconnection (HDI) PCB technology is advancing to enable increased miniaturization and functionality of products such as smartphones, tablet computers and wearable devices. This dictates continual reduction in feature size for conductor line width and spacing, micro-via pad diameter and pitch, and conductor and insulating layer thickness to accommodate more components and layers without increasing size, weight or volume of the PCB assembly. Furthermore, as wireless data transmission bandwidth and processing speed increase, electrical performance of the PCBs becomes ever more critical.

Just as the IC industry met serious roadblocks in feature scalability to keep pace with Moore's law of doubling performance improvement, so the PCB industry now faces challenges in basic process capability and material properties to continue delivering improvements in interconnection density and electrical performance on their forecast trajectories. Even in the state-of the-art process node for all-layer-via (ALV) HDI design, limitations in process scalability and escalating factory cost raise questions about diminishing returns in packaging density and performance.

In particular, the industry faces significant challenges increasing PCB layer count and reducing thickness as individual insulation layers cross the 50 micron threshold, where degradation of dimensional stability and electrical performance (particularly signal impedance and

Inspiring Innovation in...

# Flexible Circuits

Laser Processing System

IC Packaging

CornerStone

CSi CSi

UV Laser Drilling System | ICP Series 1

See Esi's patented Third Dynamics technology in UV 4 beam format. Engineered for your production environment with the highest throughput at the smallest footprint.

Designed for Brilliance. Engineered for Production.

resistance to leakage) accelerate, and increasing signal routing density below the 40 micron line width threshold where conventional subtractive technology fails and additive technology remains too costly and small in production scale to be a practical alternative.

While the increased use of sophisticated and adaptable automation such as laser direct imaging (LDI), sub 100 micron laser vias (LDD) and increased use of vision technology offer some improvements, escalating cost and hard limits in material performance suggest we need to focus on the fundamentals to make the system more robust, capable and affordable.

This paper will describe the recent challenges and developments in manufacturing ALV HDI technology to meet the needs for high volume, robust, reliable, and cost competitive solutions for electronic packaging.

### I. Introduction

As the popularity of social media surges, increasingly communication is done through smart phones or tablets. Social media is now also a crucial part of any successful businesses marketing plan. It offers us a platform to interact with existing and potential customers and can often provide us with feedback and new ideas.

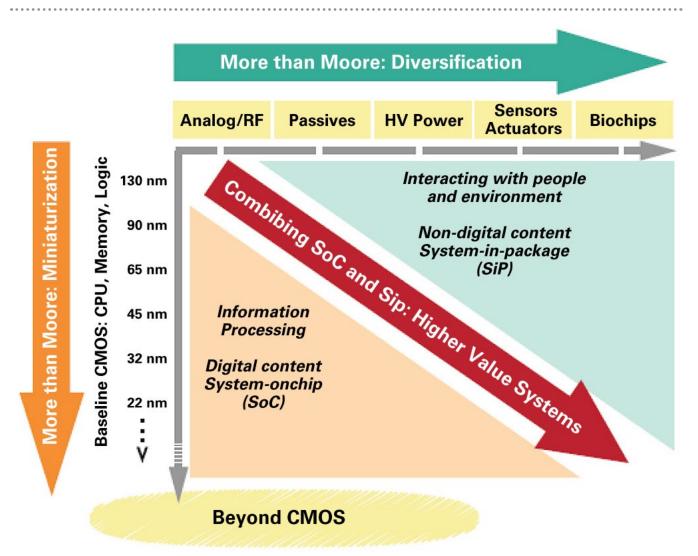

Figure 1: Illustration of applications driven by strict miniaturization according to Moore's law (More Moore), which may ultimately be superseded by novel device structures and physics (Beyond CMOS) and of applications of silicon technology providing added functionally and diversification<sup>[1]</sup>.

That means the amount of data transferred has increased considerably in recent years and will continue. Subsequent increases in functionality, together with reduction in component size, have been the main drivers for PCB development. Semiconductor technology progresses at an almost exponential rate, typically doubling in functionality every couple of years and is expected to continue at this pace for several years to come.

When comparing typical rigid PCB structure used for the first mobile phones with current state of the art PCBs for smart phones, one can see tremendous differences. It can be said that miniaturization has been the predominant trend over the years. While the external dimensions of phones have not greatly changed, component and PCB size shrink to accommodate greater functionality has been remarkable; in a typical smart phone or tablet, a majority of space is occupied by displays and batteries as the remaining electronics have been downsized and integrated into small, compartmentalized spaces<sup>[2]</sup>.

Perhaps one of the most noticeable changes has been board thinning and layer count increasing due to component pitch reduction and increase of the I/O count. A decade ago typical rigid PCB thickness was over one millimeter. Nowadays typical smart phone PCB thickness is around 0.5 - 0.7 mm but there is a clear trend that the board thickness is reducing simultaneously when the layer count is increasing. According industrial roadmaps it's expected that within the next couple of years less than 0.4 mm thick PCBs will be seen in the hand held devices, while the total number of microvia build-up layers increases to ten or even twelve layers depending on product complexity. Obviously this has led to usage of thinner dielectric and conductor layers, respectively<sup>[2]</sup>.

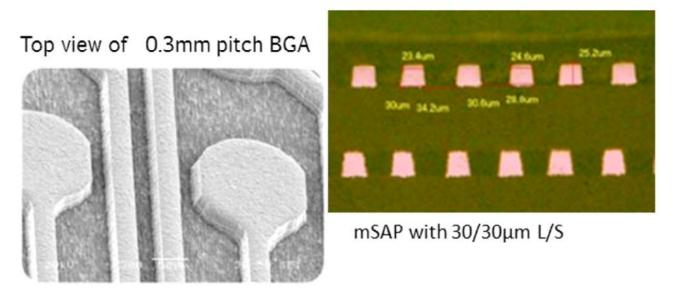

When looking at a few years back 0.6 mm – 0.8 mm pitch technology was the practice in hand held devices at the time. Today's smart phone PCBs utilizes widely 0.4 mm pitch technology driven by higher component I/O count and product miniaturization. And as expected the trend is towards 0.3 mm pitch. Indeed 0.3

Table 1: Smart connected device market by product category<sup>[3]</sup>.

mm pitch technology development work has been started several years ago for mobile terminals<sup>[4]</sup>. Simultaneously microvia size and pad diameter have been reduced being typically 75 um and 200 um, respectively. The industry is targeting to go down to 50 µm microvias and 150 µm pad size within the next few years<sup>[2]</sup>.

This miniaturization is driving the line/ space and the SMT pad size reduction in anylayer HDI PCBs. As the use of the anylayer technology is enabling the miniaturization by giving more freedom for designers allowing the connections between all layers. A capability improvement of fine line manufacturing processes is obvious and new manufacturing and processing solutions are necessary for the PCB industry to fulfill the requirement of these new designs.

### II. ALV HDI PCB Key Manufacturing Challenges

The key manufacturing steps in ALV PCB miniaturization point of view are the multilayer pressing, laser drilling, imaging, etching and plating processes, and how to optimize the process for high volume, robust, reliable, and cost effective manufacturing.

### A. Evolution of microvia laser technology

In the mid 1990s, component grid pitch dropped and difficulty encountered connecting high I/O components with multilayer PTH PCB technology. Industry responded to this challenge by developing microvia technology such as photo dielectric, plasma etched and laser drilling methods as well as reducing mechanically drilled through vias below 150 µm. However, as photovia technology needs special photosensitive material and plasma does not work with FR-4, laser drilling now predominates production due to its flexibility.

Initially, the lasers available, TEA CO2 and UV Nd:YAG had several drawbacks limiting usefulness and accuracy.

With TEA CO2 lasers of 10600 nm wave length, an inability to drill copper and unreliable galvanometers with slow rep rates and a tendency to miss pulses made it a difficult process. Copper apertures had to be etched as conformal masks or windows slightly larger than the final microvias and the long wavelength of the lasers left a thin carbonized layer that had to be removed with strong desmear.

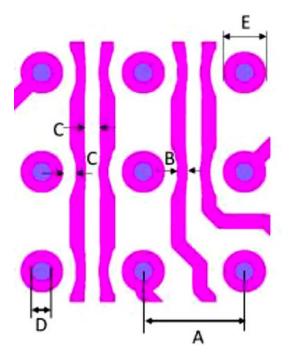

| Item                        | Mark | Design  |

|-----------------------------|------|---------|

| BGA pitch mm                | Α    | 0.3     |

| Via pad μm<br>(Inner/Outer) | E    | 150/140 |

| Line width µm               | В    | 30      |

| Space µm                    | С    | 30      |

| μvia diameter               |      | 75      |

Figure 2: Illustration of 0.3 mm pitch design guidelines.

The first UV lasers introduced in 1997 were Nd:YAG lasers @355 nm. These lasers were wellfocused with small spot diameter, so trepanning and spiraling methods were used. They were capable to cut copper and resin very nicely but had problems with FR-4 due to the poor absorption by glass. The product need to use resin coated copper as a build-up material instead of FR-4. Productivity was low and machines had issues with power stability. While stability has improved and rated power increased dramatically, glass ablation remains a problem and productivity is not comparable with today's CO2 lasers, so UV remains a niche process for special applications.

Some companies started to use UV lasers in combination with CO2 lasers. This can be answer for prototyping and small volume production but is not cost effective answer for the high volume production.

1998 marked a dramatic increase in demand of the microvia boards. In response, the mainstream PCB makers standardized etching + CO2 laser and new lasers with no missing pulses and higher rep rates were introduced to market. Productivity improvements at last made this cost effective for high-volume production. Process was also very robust and stabile. By the mid-2000s the leading edge PCB makers started to develop direct drilling trough copper. The copper is etched down in thickness to 5-12 µm and the surface of the copper is treated to be rough and dark prior drilling. The merit of this process is to reduce cost and eliminate via aperture etching. This is the leading method today for producing any layer microvias, however, the weakness is that the process window is very narrow and rework impossible. On the quality point of view it is a great challenge to have stabile production for microvia less than 100 µm with optimized microvia shape without excess copper hang, glass bundles, resin smear etc. as these will cause downstream problems in desmear and plating.

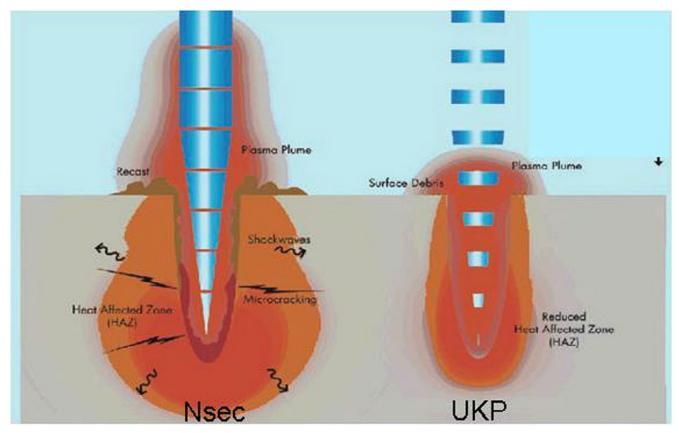

The future development of CO2 laser drilling is going to be dominating for a while. However new lasers with picosecond and femtosecond pluses are coming to market that show very promising results in speed, quality and productivity. This may be the direction where industry is going when facing the challenge of small laser via size. Thermal damage for the

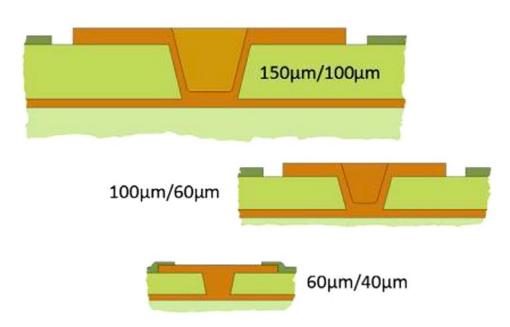

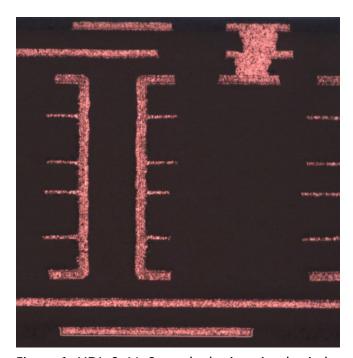

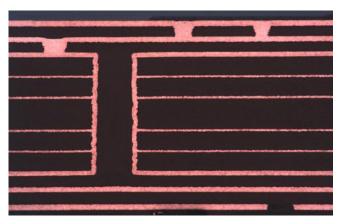

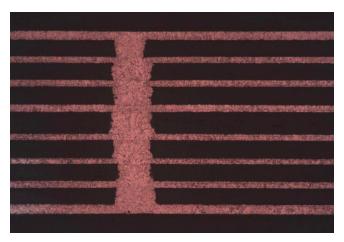

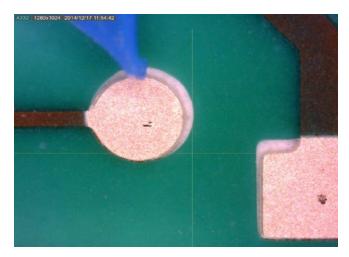

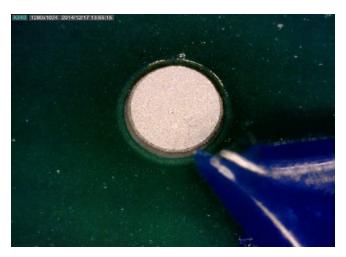

Figure 3: The top picture is 150 µm microvia with 100 µm dielectric, the typical dimensions in the late 90s. In the middle 100 µm microvia with 60 µm dielectric the typical design from early 2000. The bottom picture is today's 60 µm microvia with 40 µm dielectric.

Figure 4: Heat-effected zone to material. Nanosecond level pulses compared to ultra-short pulse lasers. Picosecond pulses reduce the zone<sup>[5]</sup>.

material is dramatically smaller than with longer pulse lasers. These new lasers work without any special treatment for the copper foil.

### B. Plating and imaging processes

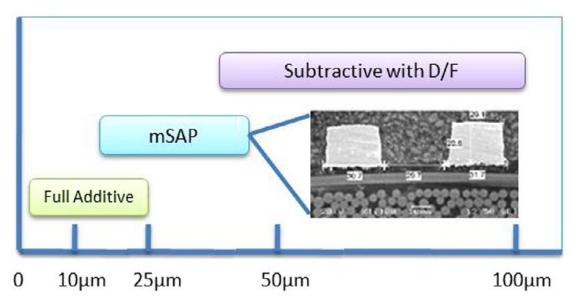

Design features e.g. line/space, dielectric thickness, final copper thickness are driving the selection of plating process (e.g., in 0.3 mm pitch BGA design with two lines between BGA pads, via hole size is normally 75 µm, and pad size is 150  $\mu$ m). Fine line with 30  $\mu$ m/30  $\mu$ m line and space is required for the layout design. It is challenging to achieve this fine line structure by existing subtractive process. The etching capability is one of the key factors where the total copper thickness together with plating uniformity needs to be optimized together with the imaging process. That is why the PCB industry is now adopting the mSAP process, which compared to subtractive process, can easily produce line with optimized conductor shape in which the top line width is almost equal to the bottom line width all over the whole production panel—easy control of the line shape. Another advantage of mSAP is that standard PCB processes such as drilling and plating are employed leveraging existing resources and know-how, and the use of conventional materials provides good adhesion between the copper and dielectric layer to guarantee the high reliability of the end product.

The key benefit of mSAP process compared to subtractive process is that it can easily produce line with optimized conductor shape in which the top line width is almost equal to the bottom line width all over the whole production panel—easy control of the line shape. Thinner conductors with controlled shape may provide some benefits in terms of signal integrity due to improved cross talk and noise ratio. In fact, moving into thinner conductor lines may be mandatory in order to reach required

# In North America Uyemura is again

### We are honored, and deeply grateful to our customers,

vendor partners and employees for making us North America's leader in PCB finishes. Thank you for an extraordinary year, and for the opportunity to be of service.

As we have since 1985, Uyemura-USA is committed to providing its customers with significant advantages in performance, cost, and maintenance, and to supporting each program with the industry's finest technical support.

Figure 5: Line width reduction vs. process technology.

Figure 6: Fundamentally higher system resolution and superior conductor geometry of mSAP process.

characteristic impedance levels due to thinner dielectric layers.

It's essential to make the optimized process selection for minimized pattern resolution and limiting build-up thickness. Plating based processes must be capable to plate/fill the holes/ vias and to produce fine patterns within design parameter sets.

Finer lines, spacing and annular ring requires much tighter controls of the imaging process. With use of finer lines, touch up rework or repair becomes an impossible task. Photo tool quality, laminate prep and imaging parameters are necessary for successful high yield process<sup>[6]</sup>. Increasingly, LDI looks attractive to replace contact exposure for this technology. While today, more than 90% of the production uses contact imaging process as LDI is slower and more expensive, LDI becomes cost effective when it improves the yield. Today's complex

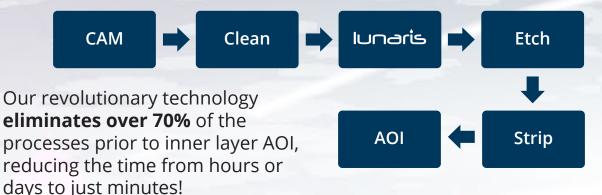

# Can you imagine CAM to etch in 5 minutes? Meet Lunaris, the first fully digital inner layer printer based on inkjet technology.

Inner layer production methods haven't changed much in over forty years. The basic process has remained the same: use lots of interdependent equipment and chemistry to completely cover a panel with photo resist. Then, use some more interdependent equipment and chemistry to remove most of it!

This is a timely, wasteful and costly process. Lunaris has a better way:

### Simplified Inner layer production flow with Lunaris

We've put together a complete guide to how inkjet technology changes all the PCB Imaging rules; get your copy today!

Download our whitepaper

Disrupting PCB imaging with inkjet technology

CLICK HERE TO DOWNLOAD

anylayer microvia boards yield improvement is essential due to long manufacturing process and fine feature sizes, so breakeven point can be reached. Leading edge smartphone boards have become difficult to produce without LDI. It offers significant benefit allowing individual scaling for panels reduction of the alignment related yield losses.

In order to get the full benefit of LDI the dryfilm and/or wet resist has to be matched with imaging technology for optimized yield. Recently there has also been significant improvement in the resist capability and productability. That might help to make the investment for LDI imaging process as there will always be a desire to use tried and tested technology when faced with a choice of some other, perhaps slower, more expensive, more problematic alternative. And still approximately 25% of new LDIs sold are used to image solder mask. DI in this particular application has the potential to bring enormous yield rewards, but is hampered by much lower throughput<sup>[6]</sup>.

### II. Summary

A closer look at key ALV HDI manufacturing processes and their impact on cost and technology benefits has to be taken in account when selecting the optimized process, and therefore, a major opportunity to meet the current and future needs of electronics packaging must be considered. The functionality increase and size reduction are not the only challenges for HDI PCBs. The increasing operating frequencies with ultrathin constructions will play a more important role in near future end products. The role of the effective supply chain management is essential to have the materials and manufacturing solution ready on time. As minimized prototype cycles result in faster product launch in the market place.

Subtractive process (foil or plating) ultimately faces limitations of nominal thickness and thickness variation and is sensitive to conductor spacing, thickness variation, and base foil roughness. Additive processes have fundamentally higher system resolution and superior conductor geometry but are complex to engineer/ control and might require capital investments. The conductor geometry of mSAP has superior signal integrity with lower loss and crosstalk due to straight sidewalls.

There is no easy answer for manufacturing process selection as it depends on the product design features. Early involvement in design process is helpful for finding the most cost effective solution. **PCB**

### **Acknowledgment**

The authors would like to thank Chris Katzko for his timely support and contribution.

This paper was originally presented at the 2014 Electronic Circuits World Convention.

### References

- 1. Joachim N. Burghartz, Editor, "Ultra-thin Chip Technology and Applications," Institut fur Mikroelektronik Stuttgart (IMS CHIPS) Allmandring 30a, Germany, pp. 17, April 201.

- 2. Erkko Helminen, Tarja Rapala-Virtanen, "Miniaturization Influence on Electrical Functionality of High Density Printed Circuit Board" 'in press' ECWC13, 2014.

- 3. International Data Corporation (IDC), Worldwide Quarterly Smart Connected Device Tracker, 2013-Q3 edition, 2013 September 11; Smart Connected Device Market by Product Category.

- 4. T. Katahira, J. Scanlan, J. W. Park, K.S. Oh, "0.3 mm Pitch CSP/BGA Development for Mobile Terminals," International Microelectronics and Packaging Society, IMAPS, November 11–15, 2007, San Jose, CA, USA, pp. 393-401.

- Kunz, 5. Stephan Schmoll-Maschinen GmbH, EIPC Winter Conference Geneva, Switzerland, January 30 & 31, 2014.

- 6. JPCA 2014 Show Technology Summary.

Tarja Rapala-Virtanen is in technology at TTM Technologies Inc., Asia Pacific, China.

Erkko Helminen and Timo Jokela\* are in technology/R&D with TTM Technologies Inc., Asia Pacific, China/Finland\*

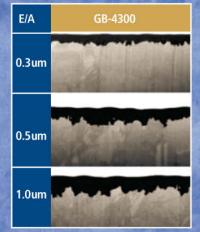

**Electronic Chemicals, LLC**

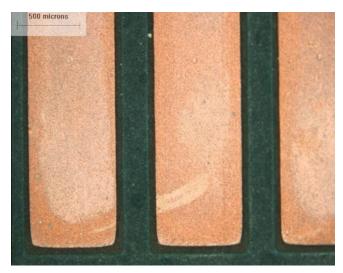

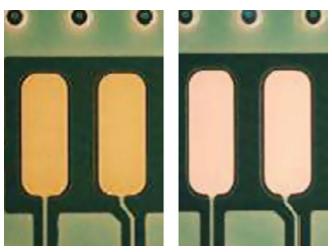

**Copper Roughening Process** for SM & IL Adhesion **Promotion**

Lower Profile for Signal Integrity and Final Finish **Appearance**

### **Advantages:**

- Sulfuric-Peroxide selective micro etchant for Cu foil and electroplated Cu panels

- 3-step process that is economical and environmentally friendly

- Recommended for Solder Mask, Dry Film resist, Coverlay and Substrate processes

- Lower etch amount required than competitive processes

### **Outer Layer** TECHNOLOGY

Before GB-4300

After GB-4300

Competitor

### We've Got the Whole Process Covered

# **High-Density** Interconnects: **Enabling the** Intelligence of Things

by William Beckenbaugh, Ph.D. and Joan K. Vrtis, Ph.D. MULTEK TECHNOLOGIES LTD.

#### Abstract

The rapid evolution of high-density interconnects printed circuit board (HDI PCB) technologies over the last five years has been accelerated largely by the mass production demands for global deployment of 3G and 4G mobile phone products at attractive consumer pricing. The major capacity expansions in Asia factories has allowed circuit shipments at the highest volumes and quality levels yet experienced since the invention of the circuit board in the 1950s.

As the Internet of Things (IoT) spawns new intelligent connected platforms (IP) for sensing and control products such as wearable electronics, home automation, and medical monitoring, HDI processing is being applied to rigid-flexible printed circuits (RFPC) and multilayer flexible printed circuits (FPCs), modified in new ways to achieve mechanical, physical, and chemical exposure robustness and low latency communication to the cloud. The purpose of this article is to explore the key requirements and new approaches required for the application of HDI, especially stacked, copper filled microvia pro-

cessing of thinner, low loss materials, to achieve the routing and solder joining capabilities required by advanced surface mount technology and final assembly techniques dictated for

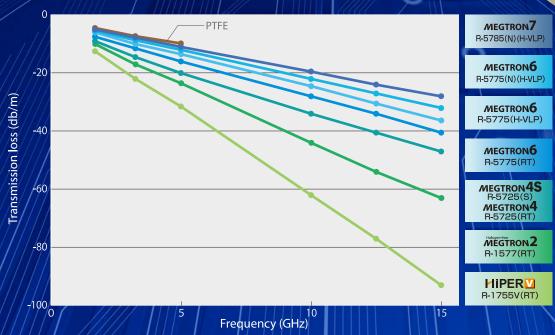

## **Panasonic**

For ICT infrastructure equipment

# Low transmission loss

multi-layer circuit board materials

# MEGTRON series

■ Frequency dependence of transmission loss

**Contact us**

**More information**

HDI layers and

sub-composites with

laser drilled vias

combined with stacked.

copper filled vias up to

16 layers has become

the state of the art in

circuit design for the

newest generation of

mobile phones, wearable

electronics, and

IoT modules.

leading edge semiconductor component packaging densities.

### **Background**

Beginning in the 1980s, the electronics industry began the early days of transition from pin-in-hole wave soldering to surface mounting of increasingly complex semiconductor packages. Strategic technical analysts at companies such as IBM, Bell Labs (Western Electric), Digital Equipment, Hitachi, NEC, and Hewlett Packard realized the existing PCB processes and materials faced an impending industry-wide capability bottleneck with urgent implications in limiting copper trace and solder pad featuring. From this exigency came the industry-wide invention of a continuing variety of microvia processes and production systems that continues to this day. Today, the copper filled, stacked laser drilled microvia multilayer process is the dominant in global production.

In a parallel but separate roadmap, the flexible circuit has evolved since its inception as an early alternative to cabling and power distribution. Flexible printed circuits evolved quickly in the early 1980s to become the dominant form factor for very fine-pitch semiconductor packaging substrates and liquid crystal display interconnection. With reel-to-reel mass production lines adapted for wet chemical and fine-line lithographic techniques, FPCs continue to be an essential element in product design solutions today, especially for touch screen and large area LCD and LED based displays.

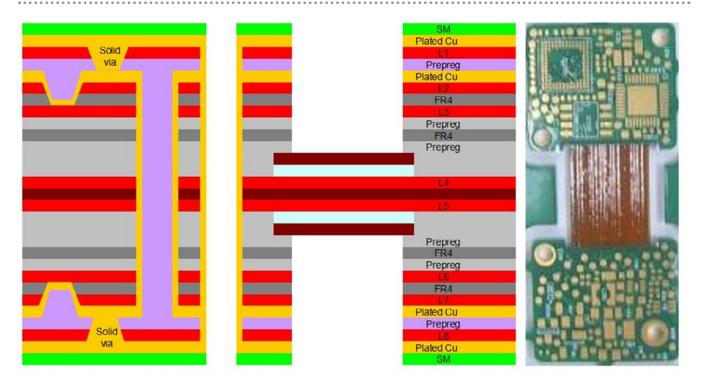

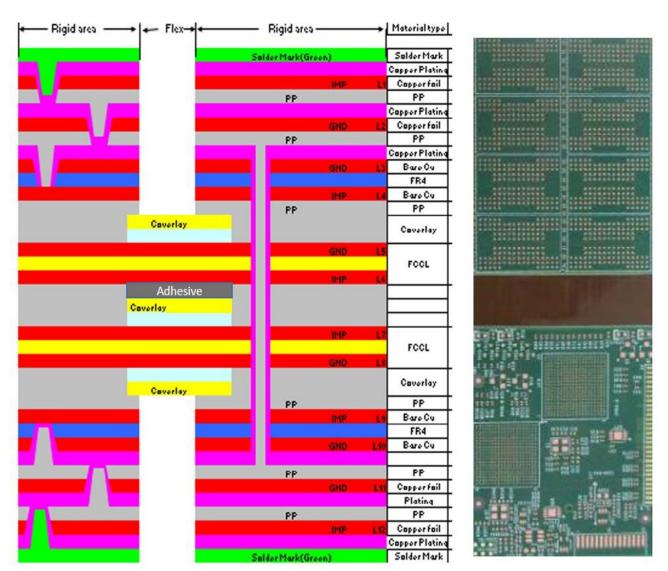

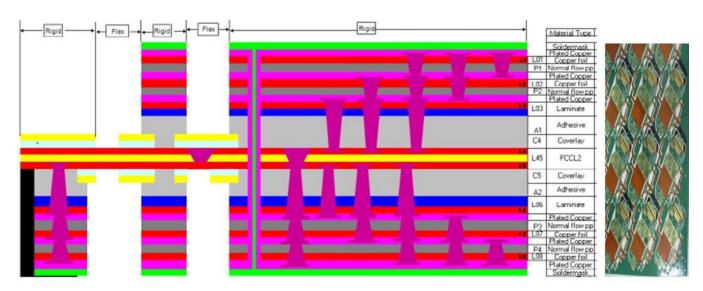

The HDI-FPC hybrid platform, known as rigid-flex or RFPCs, has been adapted to a number of different stackups to solve designers' interconnect-product structuring challenges, resulting in an extensive patent literature of innovation. In general, one or more fine line single or double sided FPCs are applied as the conformal

connection planes in a stackup combining HDI rigid PCB inner and outer layers, and appropriate adhesives and coverlays to both combine and protect the core for laser via creation, as well as final plated through-hole (PTH) and final metal finish plating steps. HDI layers and sub-composites with laser drilled vias combined with stacked, copper filled vias up to

16 layers has become the state of

the art in circuit design for the newest generation of mobile phones, wearable electronics, and IoT modules.

### **High-Density Interconnect Stackup Basics**

The increasing need for greater functionality in a small form factor drives the HDI PCB stackup designs.

The interconnect structures in HDI PCB include buried vias and microvias. In standard HDI, such as a 1+N+1 and an i+N+i stack up, both buried vias and microvias are used. Every layer interconnect connection (ELIC) uses only stacked copper filled microvias. Each of these stackup structures enable designs for smart, connected devices and the choice of HDI struc-

tures is dependent upon several factors including functionality, connectivity, product dimensions, weight, reliability, assembly requirements and user experience.

Table 1 provides a high-level definition and comparison of the HDI Stackup structures.

Buried vias may be drilled into just one internal core that connects the top and bottom layer or into a multi-layer subpart. These buried vias connect multiple layers together internally using standard through-hole requirements for annular ring, aspect ratio and drill to copper requirements.

Stacked microvias are just as it states. The vias are laser drilled one on top of the other in adjacent layers creating a stack of microvias in the PCB. For best reliability, it is recommended that only copper filled microvias be used

# WorkCell<sup>2</sup> Vacuum Lamination System ... A Modular Design That GROWS With You

With the ability to expand as production needs dictate, Bürkle's modular WorkCell<sup>2</sup> provides a precision Vacuum Lamination System for every phase of business – from start-ups to high-volume production houses – we have the right system for you.

The Bürkle WorkCell<sup>2</sup> is part of Bürkle's wide range of laminating and coating systems. Bürkle is a member of the Bürkle North America alliance with Schmoll-Maschinen, Bürkle GmbH, IMPEX, LHMT and Bacher Systems. For more information contact Bürkle North America via e-mail: sales@burkleusa.com.

Alliance partner web sites:

- · www.schmoll-maschinen.de

- www.buerkle-ambh.de

- www.bacher-systems.com

- www.impex.co.at

- www.lhmt.de

Bürkle North America, Inc.

12802 Valley View St., Ste. 12/13 Garden Grove, CA 92845

TEL: 714-379-5090 FAX: 714-379-5092

WWW.BURKLEUSA.COM

when stacking. Stacked microvia can be combined with buried and thru-hole technology (Figure 1).

Staggered microvias are laser drilled offset to the other microvia in adjacent layers creating a staggering pattern of microvias between layers in the PCB. The microvias do not necessarily need to be copper filled and are often resin filled from the adjacent dielectric layer. Staggered microvia can be combined with buried and thru hole technology (Figure 2).

Every layer interconnect connection (ELIC) allows for dynamic connection between any two layers within the circuit layout. This flexibility optimizes useable area for dense component placement and provides a higher level of circuit density for complex routing challenges. ELIC employs a method of using stacked microvias on every layer. This process starts with an ultra-thin core that has microvias drilled and solid copper filled as the base. Using this initial core, a sequential lamination is use to add additional dielectric layers with laser drilling and copper via filling as required on both sides to achieve the final stackup (Figure 3).

This allows for the unique process of starting and ending any routing requirement on any layer and opens routing channels and provides the ability to reduce the overall thickness of the PCB. ELIC design guidelines follow the same structures as for stacked microvia, but provide higher internal routing density due to the elimination of buried through-hole vias in the initial sub buildup, and eliminating holes

| Stack Up<br>Structure<br>Designation                      | Define                                        | Structured                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1+N+1 High-density routing on top and bottom layers only. |                                               | Outer Layers: HDI formed using laser drilled microvia, copper filled.                                                                                                                                                                                        |

|                                                           |                                               | Inner Layers:  N* interconnected by a buried via, a mechanically drilled thru-hole, copper plated and polymer filled.  * N is the number of inner layers.                                                                                                    |

| i+N+i                                                     | HDI on 'i' number of outer layers where i >1. | Outer Layers: Greater than one HDI layer formed using laser drilled microvias*, copper filled. *Microvias can be stacked or staggered.  Inner Layers: N* interconnected by a buried via, a mechanically drilled thru-hole, copper plated and polymer filled. |

| ELIC                                                      | High-density routing on every layer.          | * N is the number of inner layers.  Every Layer Interconnect Connection: stacked microvias on every layer. The microvias are 100% copper filled.                                                                                                             |

Table 1: Typical stackup structures of HDI technology.

Figure 1: HDI: 2+N+2, stacked microvias, buried through-hole via.

in layers not requiring for routing in the design (Figure 4).

Multek has made extensive investments since 2004 in the invention and production scaling of customers' ELIC requirements, with

Figure 2: HDI: 2+N+2 staggered microvias, buried through-hole via.

# MULTEK Every Layer Interconnect Connection Technology Inner core with laser microvia Special copper microvia plating – solid via Standard HDI lamination and laser drill Special copper microvia plating - solid via Standard HDI lamination and laser drill Special copper microvia plating - solid via

Figure 3: ELIC sequential lamination steps to form solid copper stacked microvias.

additional process engineering to implement core FPC processing into HDI rigid-flex designs now required by our customers with wearable and IoT circuit and module designs.

### **HDI: Enabling Technology for the Intelligence of Things**

Flextronics has recognized that IoT is rapidly evolving to The Intelligence of Things to

Figure 4: Every layer interconnect connection, 8-layer rigid.

become a new ecosystem of smart, connected devices, machines and systems that interact to deliver greater capabilities, efficiencies, and experiences are changing the way we live, work and play. The innovation landscape driving The Intelligence of Things will increasingly propagate smart, connected products due to the adaptation of the core HDI interconnect platforms of rigid and flexible PCBs.

### **Miniaturization:**

HDI enabled the miniaturization of the printed circuit to address the demand for increasing functionality yet smaller form factors in mobile communication devices (i.e. cellphones and tablets). Another driving factor for HDI is increasing power requirements resulting from the additional functionality and also the growing size of the color display. These additional power requirements resulted in larger battery footprints. This accelerated the HDI adoption as the larger battery dimensions were expanding and the PCB size needed to shrink to accommodate the overall product outline. Early cellphone PCBs were X layer, standard thruhole via technology and X mil lines and space

Figures 5: Stack-up of actual RFPCs using HDI technology in automotive application.

# Direct Image Solder Mask

### **EMP110 DI**

Carapace® EMP110 DI is the next generation in Liquid Photoimageable Soldermask for Direct Imaging.

- Suitable for Laser and LED Direct Image Systems

- Versions available for 355nm up to 405nm light sources

- Low Exposure Energy (down to 50-80 mJcm<sup>-2</sup>)

- Fine Solder-dam Resolution (50 micron, 2mil)

- High Chemical Resistance to ENIG & Sn Processes

- Screen-print and Spray

- Halogen-free, RoHS and fully REACH compliant with no TGIC or other SVHC content.

Optimised radiation curing characteristics deliver high levels of through-cure and straight side-walls at low energy levels without compromise in surface tack or chemical resistance.

www.electrapolymers.com

and average total thickness of 0.062 inches. Current mobile communication products such as Smart phones have HDI technology can be up to 14 layers, ELIC technology, 50 micron L/S inner layers, 37.5 micron L/S outer layers and total PCB thickness from 0.060 to 0.047 inches, based on core and pre-preg thickness options.

Smartphones presently have the functionality of a personal computing, high-resolution camera and video, transmission and receipt of data, and, yes, phone capabilities. The smartphone is now the hub of personal and device connection.

### The HDI Building Blocks for Smart, **Connected Products**

HDI PCBs and HDI-FPC hybrid platforms are key building blocks in multiple applications across automotive, medical, data & storage, mobile communication and wearable technologies.

There are multiple benefits and advantage of HDI-RFPC hybrids that includes:

- a) A single printed circuit with repeatable, reliable, high density interconnects.

- b) System cost-saving resulting from component integration (eliminates connectors and other components).

Figure 6: Stack-up of actual RFPCs using HDI technology in data storage application.

### **CP 6080**

### LOW COST DIGITAL INK JET PRINTER

CCD CAMERA **ALIGNMENT**

a printing legend

- Up to 4 Colours depending on type of ink

- Vacuum-Table for hold down of flexible materials

- In line UV Curing

- CCD camera for accurate alignment

- Tooling pin registration

- 180 1440dpi

PRINT BAR CODES

LEGEND INKS • ETCH RESIST • UV BLOCK

Figure 7: Stack-up of actual RFPCs using HDI technology in wearable technology application.

- c) Elimination of wiring connections errors during installation and servicing, reduced assembly labor.

- d) Three dimensional packaging where the flexible circuit can be bent to fit individual products to be installed in non-planar space.

- e) Minimized weight and space, 75% less weight of conventional wiring type connection between multiple PCBs.

- f) Improved reliability through elimination of connectors and reduced thermal stress on solder joints.

- g) Thin, flat conductors and thin insulation resulting in improved thermal dissipation.

- h) Greater electrical performance for consistent electrical impedance performance with integral ground planes.

- i) Uniform electrical characteristics with consistent conductor spacing and insulation parameters.

### Summary

From its inception, the printed circuit industry's success factors have been inventive response to new product designs' performance, reliability, and cost requirements. With the creation of the global cellular communications infrastructure over the last 20 years, Internetenabled wireless communication and computing products have become an essential part of the fabric of life across the globe. Yet, this recent past is only a prologue to the major impact that the current expansion of the connectivity matrix between humans and smart devices and products will foretell. For example, the ELIC examples we have shown in this article took the global PCB industry a decade to evolve from early process concepts.

Industry leaders from all parts of the PCB supply chain must do more pre-competitive partnering to create and optimize the best solutions more quickly than in the past. At Multek, we expect that the rate of scaling of the next core processes, equipment, and materials envisioned for the massive deployment IoT designs must follow a more aggressive timeline of collaborative setting of new interconnect technology direction and investments. PCB

William Beckenbaugh, Ph.D., is technical advisor at Multek Technologies.

Joan K. Vrtis, Ph.D., is chief technology officer at Multek Technologies.

that are Unique in the PCB Marketplace

Many new materials in our industry do what others do with only some incremental gain.

Insulectro's unique Six Pack Performance Products offer unprecedented opportunities to solve big problems in PCB design and fabrication. There's nothing like them.

### **CHRONON™**

Isola's latest laminate with electrically transparent glass fiber reinforcement to eliminate differential pair skew for your next generation High Speed Digital designs that operate above 10 GHz.

### CONFORMAT™

LCOA's conformal drill layer is soft enough to overcome image transfer challenges, yet hard enough to exit side suppress burrs in the drilling process.

### ORMET SINTERING PASTE

Ormet Circuit's Z-axis interconnect paste that forms a metallurgical bond to circuit traces between layers and facilitates both rapid time to market and high complexity boards.

### **PYRALUX® HT**

DuPont's laminate system with a service temperature of 225°C for flexible and rigid PCB applications, allowing previously impossible designs for automotive, aerospace, oilfield and other high temperature environments.

## THERMO PAD/FILM

Pacothane's high temperature press pad and film which utilize a unique release technology for temperatures up to 300°C, allowing reliable lamination of the latest generation of game changing high temperature materials.

## **POLYIMIDE SILVER PASTE**

Coming soon!

insulectro.com

Insulectro's World Class Suppliers

# **Splitting Hairs:** The Manufacture of HDI and Substrate Test Fixtures

by Todd Kolmodin **GARDIEN SERVICES**

Testing of higher-density product has become ever more challenging with the advancement of chip technology. BGAs, CCDs and other active components have decreased in size so much that historical industry accepted test methodology can no longer effectively test these newer substrates incorporating this higher technology.

Universal grid test machines in North America, for the most part, are limited to single and double-density grids. Dedicated (wired) fixtures can combat some of the density issues faced in today's test arena, but to successfully succeed in the high-volume demand market a test solution must be found to efficiently test the product and also provide automation to reduce cost.

Universal multi-plate fixtures routinely use test pins down to .3 mm. As pin size decreases, the need for extra plates in the fixture increases, so as to stabilize the pin and provide accurate loading of the pin. However, critical mass is soon reached as the fixture can no longer be solved due to inadequate grid contact availability. Further, as the density is maximized the fixture loses internal support and finally becomes unstable producing false defects, excessive troubleshooting and lost time.

Additionally, there is an ever-increasing demand for 4WK measurement especially on HDI boards, requiring two probes contacting the same pad simultaneously, which can only be

Atotech's Inpulse 2HF – The Low Cost Solution for Blind Micro Via Filling

Diameter 170  $\mu m$  / Depth 100  $\mu m$  Plating thickness 15  $\mu m$  Plating time approx. 30 min Dimple < 10  $\mu m$

#### The Process

- Conveyorized metallization and plating system

- Proven in high volume HDI production

- Inpulse 2HF with insoluble anodes gives longest electrolyte lifetime in full production

- Superlative filling results with minimum surface plated copper

- Filled BMV with less than 5 μm dimple

#### Savings

- 50% less plated copper on surface

- Reduced soldermask consumption

- Reduced etching process consumption

- Minimum processing time for filling

- Less wastewater treatment

### **Features and Benefits**

- High productivity

- Excellent surface uniformity

- 2 MIL line and space capability

- Lowest possible surface Cu plated for BMV filling

Filled stacked BMV for mobile phone production with Inpulse 2HF and SuperFilling

Increase Productivity/Performance

**Start Saving Now!**

Material Usage Decrease

### SPLITTING HAIRS: THE MANUFACTURE OF HDI AND SUBSTRATE TEST FIXTURES continues

tackled, especially for volume production, with this or similar technology.

### **HDI Fixtures vs. Substrate Fixtures**

Quad and octal density universal equipment is used for standard HDI fixturing. Pin sizes for this type of fixturing are usually 90–110 µ with a length of 20-30 mm, therefore much smaller and shorter than standard universal grid fixtures. To put this in to perspective the human hair has an average diameter of about 70 µ (micron.) Pins in a substrate fixture of current generation typically are 70–50 µ; the next generation under development will reach 40-25 µ.

Substrate fixtures are typically not used with universal test machines. They require a much higher grid density; therefore the grid itself is generated as a wired solution either to standard connectors or to a universal one-touch interface depending on the final machine used.

HDI fixture usually test a complete test array, whereas substrate fixtures usually test only one or two images of the entire array and the machine will step the board through in multiple tests. That is mainly done to achieve the high accuracy required to test those kinds of boards and the extreme cost and time involved to make these fixture.

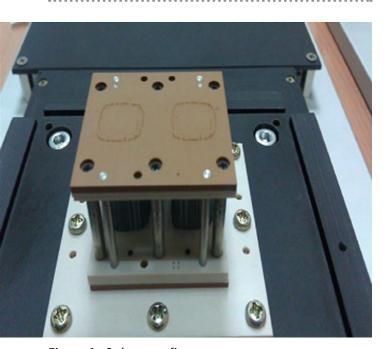

Figure 1: Substrate fixture.

HDI fixture typically can be produced within 48 hours, the manufacturing time for a substrate fixture is usually 100-200 hours, and extreme cases can even take longer.

The manufacturing process for the substrate fixture is much more complex than the standard universal fixture. Accuracy is absolutely critical for the success of registering the product to the fixture.

There are basically six steps in the manufacturing process whether it is a hybrid design or a tension probe design:

- 1. DFM—Engineering

- 2. Drill

- 3. Electrode level—wiring, electroplating

- 4. Probe level—adding probes (wires)

- 5. Final assembly

- 6. Final QC and test setup

### **Engineering**

In this step the test engineer utilizes CAD/ CAM tools to design the fixture. This includes the intelligence for the test machine, the wire mapping for the fixture and the programs for the CNC drill machines.

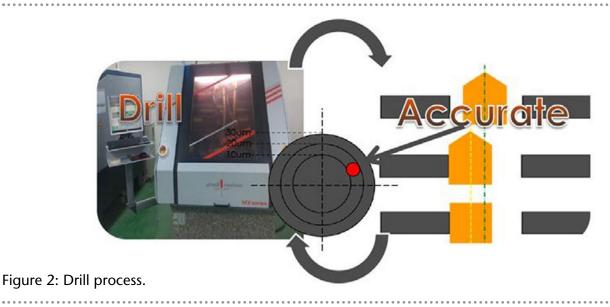

### Drill

The next step involves the drilling and machining of material to be used. The material used can be FR-4 for HDI fixture but is typically material without glass fiber enforcement for the substrate type. Accuracy is crucial in this phase. The plates are drilled and the holes are then optically measured for positional accuracy and size. Figure 2 illustrates the process.

### **Electrode Level—Wiring and Plating**

In this process the actual wiring takes place. Using the wire maps the cable assembly is produced which will interface to the test machine on one side and the test pins on the other. This process is very delicate and requires a high skill level. Electroplating is used to combat oxidation on the critical test area so that functionality is not degraded over time.

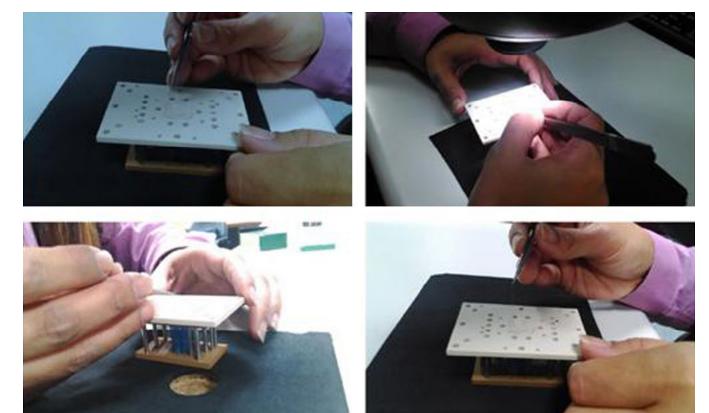

### Probe Level—Adding Probes/Pins

In this stage the probes are added to the fixture. Due to the small size of the actual probes/

# THE MOST IMPORTANT POINTS IN MULTILAYER ALIGNMENT ARE

ACCURACY

TOUTH ACCURACY

ACCURACY

ACCURACY

## **DIRECT OPTICAL REGISTRATION**

The only system on the market that will cut the layer to layer alignment tolerance in half of the best pin process available—and we have the customer data to prove it!

34 layer panel with thin core and subs in the final stack-up

DIS, Inc. 85 Hoffman Lane, Suite Q Islandia, NY 11749 Des

Designed, Patented and Made in U.S.A.

For more information email: sales@distechnology.com

(631) 851-0102 www.distechnology.com

### **SPLITTING HAIRS: THE MANUFACTURE OF HDI AND SUBSTRATE TEST FIXTURES** continues

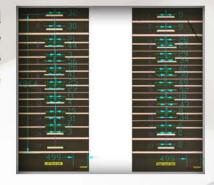

wires this is a manual process. Each probe is installed one at a time (Figure 3). There is no automated option for this step due to the finite and delicate nature of the probes/wires being used. A steady hand and in many cases magnification is required during this critical step.

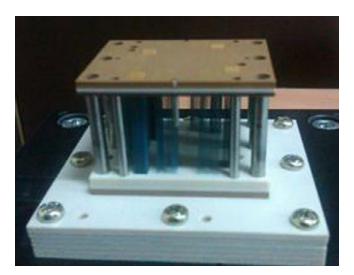

### **Final Assembly**

In this step the mechanical pieces are brought together. All the machined parts are brought together with the delicate probe/wire module. This is a critical step as all tolerances must be within nominal parameters or the final

Figure 3: Probe installation.

## The very best in PCB supplies and equipment

## "Don't forget the Phototool - just YET!"

Despite continuing growth of Direct Imaging, many companies still rely on the Phototool to process their primary imaging and solder mask boards.

Matrix and AGFA are combining forces to help customers review their current silver processes and bring them back into specification.

Faulty Phototools can lead to costly yield losses:

- Pin holes in critical fine line circuits

- Poor line edge quality can lead to improper stripping and plating shorts

- Dimensional instability can lead to poor hole and layer registration

## Call Matrix today for a Phototool evaluation.

We will bring those forgotten film processors back up to speed.

Supplier to the North American Circuit Board Industry since 1977 Canada

1124 Mid-way Blvd. Mississauga, ON L5T 2C1 P (905) 670-8400 N. California

3261 Edward Ave.

Santa Clara CA 9509

Santa Clara, CA 95054 P (408) 477-2963 S. California

301 West Dyer Rd, Suite E Santa Ana, CA 92707 P (714) 825-0404

800-668-5447 • www.matrixusa.us

### SPLITTING HAIRS: THE MANUFACTURE OF HDI AND SUBSTRATE TEST FIXTURES continues

Figure 4: Assembly.

product will not perform as required. Figures 4 and 5 show the final assembled fixture.

## **Final QC and Test Setup**

This is the final phase of the process. The fixture is setup up on the test machine and tested for proper operation. The wiring is verified and if any faults are found they are corrected. The unit under test (UUT) is then introduced to the fixture. Due to the extreme density and required precision of the alignment two different methods are incorporated. Typically for a substrate fixture an optical alignment process using pre-determined fiducials is used. This views the UUT once placed on the test head and can make corrections in both X, Y and Theta. For HDI fixture, either the process is the use of an electrical alignment system where an electrical stimulus is applied to pre-determined features on the actual UUT or a combination of both is used. Again, X, Y and Theta corrections can be made to guarantee proper and accurate probing of the features of the UUT. Once this process is complete the fixture is ready for production use.

### Summary

As can be seen above the HDI and substrate fixture technology is truly an art form. Long gone are the luxuries of just using a plated drill file on an old drill machine and automatically dropping pins. Even the multi-plate fixtures that are used today have no comparison to the criti-

Figure 5: Assembly.

cal manufacturing requirements of the HDI and substrate fixtures. North America has yet to see much of this type of volume testing at the bare board level but in Asia it has become commonplace. I was able to witness this type of technology while visiting a few shops in China. Watching the sheer volume processing utilizing automated equipment and HDI/substrate fixturing was very impressive. The care and attention to detail required to successfully manufacturer and further test this type of product is truly for the patient and steady handed engineer/technician. This is the wave of the future as chip packagesget smaller and smaller. Just think, as the pins get down to 25 µ the human eye will have trouble even seeing this pin without magnification and since the human hair is roughly 70 µ we will truly be splitting hairs! PCB

Todd Kolmodin is the vice. president of quality for Gardien Services USA, and an expert in electrical test and reliability issues.

## **Electronics Industry News**

## Market Highlights

## **Gartner: Smartphone Sales Tops One Billion Units in 2014**

Worldwide sales of smartphones to end users had a record fourth quarter of 2014 with an increase of 29.9% from fourth quarter of 2013 to reach 367.5 million units, according to Gartner, Inc. Samsung lost the No. 1 spot to Apple in the global smartphone market in the fourth quarter of 2014.

## **Wearable Tech Market to Reach** \$70B by 2025

There will be over 3 billion sensors in wearable technology devices by 2025, with more than 30% being emerging sensor types. Wearable Sensors 2015–2025: Market Forecasts, Technologies, Players is a brand new IDTechEx report which provides the only up-to-date and specially tailored analysis of every prominent sensor type for wearable technology.

## **China Eyes Bigger Share in Mobile Phone Display Market**

According to a new report from IHS, the leading global source for critical information and insight, Chinese display module makers have resolved to increase their share of global mobile-phone display shipments. In Q3 of 2014, BOE unseated Samsung Display to become the leading global mobile phone display module supplier.

## **WLAN Market Witnessed Sluggish** Growth in Q4 2014

According to the results published in the International Data Corporation (IDC) Worldwide Quarterly WLAN Tracker, the enterprise segment continued to grow at a steady rate and increased another 7.4% over the same period last year. After an uptick in year-over-year growth in 3Q14 (9.4%), the enterprise WLAN market growth rate resumed a pattern of incremental growth rate decreases.

## **Passive Optical Components Market** to Hit \$38B by 2019

The report states that the worldwide market for passive optical components stood at US\$10.01 billion in 2013. Registering a CAGR of 21.1% from

2014–2020, the passive optical components market is projected to reach a total worth of US\$38.19 billion by the end of 2020.

## **Transition to Welding Robotics** is Inevitable

Modernisation needs in the competitive global market and the rising emphasis on energy efficiency are steering industries towards automation. This trend is driving the uptake of welding robots over manual welding methods.

## \$1.36T Market Potential of Increased **Digitization**

The increased use of digital technologies could boost productivity for the world's top 10 economies and add US\$1.36 trillion to their total economic output in 2020, according to a new study by Accenture. The study is based on the Accenture Digital Density Index, a tool that helps companies make better strategic investments based on granular measures of digital performance.

## PMI Experienced Loss in 2014 but **Expects Better 2015**

Probe Manufacturing Inc. (PMI), a Product Development Accelerator providing engineering and manufacturing services to innovative technology companies reports sales of approximately \$3,550,000 and gross profit margin of \$920,000 for the year ended December 31, 2014.

## Small Business Slows in February

U.S. small businesses added 15,000 new jobs in February, making for more than 910,000 jobs added since March 2010, but revenues per small business decreased by 0.2% in January, which translates to a decline of 1.8% when annualized, according to Intuit.

## **U.S. Economic Growth Seen to Continue**

UCLA Anderson Forecast's first quarterly report for the U.S. economy says that the nation "looks like an island of stability in a very volatile world." The implication is that the U.S. is still on track for 3% GDP growth for the next two years, despite slow growth and currency devaluations throughout much of the rest of the developed world.

I-Connect007 Publisher Barry Matties and recently-appointed Multek CTO Dr. Joan Vrtis sat down at IPC APEX EXPO 2015 to discuss the rapidly evolving wearables market, especially for medical, and the myriad questions that must be addressed. Other topics include Multek's contribution to the wearables industry and what it sees as the main challenges to putting their circuits into various applications.

**Barry Matties:** Why don't you start by telling me a little bit about what's that like being chief technology officer at Multek. I understand it is a recent position. Congratulations!

**Dr. Joan Vrtis:** Thank you very much. Multek is an industry leader in printed circuit technology, and the wholly owned subsidiary of Flextronics. As the chief technology officer, I'm looking at the wearable technology and how we can put our printed circuits into

applications. So for Multek, it's really the solutions of what we can offer on the printed circuit side, whether it's a rigid circuit, a flex circuit, a r igid-flex and even things that can stretch and bend. We must be prepared for the broad markets we serve, specifically in the wearables.

That's currently where I've been putting most of my effort.

Matties: Wearables is a fast-moving market, isn't it?

**Vrtis:** Yes, it is.

**Matties:** What is the state of the market as you see it, currently?

Vrtis: One of the things we've seen just recently is the expansion of the number of ideas as to what should be a wearable. How do we help translate these ideas to product and how do we market them? Some trends regarding wearables are in close proximity to the body, on the body and in the body. For example, the wristband type of technologies, such as activity band, watch, smart watch. Then there are the wearables on skin, which includes patchlike technologies used for authentication. Now, wearables ideas are growing, as inventors and companies look at putting electronics into a fabric. Can the button be used as the connection for the continuity of the circuit? Can the zipper be part of the solution to turn on and off the electronics if placed in a safety jacket? How do we integrate the components that go with that? We have to consider power, wireless, etc. And if you want something that's going to move—a gyroscope, or accelerometer—how do

## The latest in hole filling at Taiyo

VISIT OUR

BOOTH AT

PRODUCTRONICA

MUNICH - NOVEMBER

## THP®-100DX1 (HTG)

## Thermal Curable Hole Plugging Ink

- High Tg (173°C) and Low CTE (20/56 ppm)

- 100% Solids for Extremely Low Shrinkage

- No Chemical Attack through Desmear

- Halogen-Free and RoHS Compliant

- High PCT and Thermal Resistance

- Designed Specifically for Automated Hole Filling Equipment and to Fill Small Vias Without Voids and Sagging

12.5 :1 Aspect Ratio

**Used with Controlled Depth Drilling**

Phone [775] 885-9959 • www.taiyo-america.com • info@taiyo-america.com

### THE CHALLENGES OF THE FAST-MOVING WEARABLES MARKET continues

we put all of these components in and how do we select those components?

On the printed circuit side, historically we're used to circuit boards being like 2D structures, thus they would be flat, and then we would place the components on and go. But now we also have to take into account that they're going to bend and move. When it starts getting into the apparel side, do you make that cloth fabric your printed circuit substrate? Those are the things that people are coming to us with and saying, "Hey, can you guys do apparel?" But what does that mean? Are you going to wash it? There are a lot of questions to ask.

**Matties:** With the power technology in apparel and wearables, certainly washing must be a big issue.

**Vrtis:** Yes, it is a big issue, as is drying.

**Matties:** What's the craziest thing that someone has approached you with?

**Vrtis:** Let's see. I've had some very interesting requests for solutions with the printed circuit, but the craziest probably doesn't need to be recorded here.

Matties: That's okay; we can leave it to the imagination.

Vrtis: The important thing is that they needed all of the same components I have

been talking about. They needed power and they needed some way to have this wireless to connect.

**Matties:** Let's talk about the market a little bit. What's the size of the market right now, the way you are seeing it?

**Vrtis:** Wow, it's in the billions! I've read eight billion is predicted in the next couple of years.

**Matties:** Where was that just a few years back?

Vrtis: It was a twinkle in the eye. It started with these activity band-type systems. I think Nike was one of the first, and I'm not promoting any product, but I recall as a runner, you would put the accelerometer in your shoe and if you had an iPhone, it would connect to it. Then Nike put it on a wrist. It was a very interesting transfer of the product. If you look back in time and you think back to the 1960s, one of the first things I remember in wearables was the feedback technology. Take the mood ring, for instance. The mood ring, if you think about it, was a wearable device that could tell the mood of the person based on a thermotropic technology system. That was the first one that I remember, but electronically, my experience was probably running with the Nike band.

Matties: You have talked about flex and all the challenges in the field. But in terms of manufacturing wearables, what are your challenges?

Vrtis: As I stated, almost everything we've done in the past have really been 2D, flat printed circuits, where you place it in the end product and the printed circuit never moves again; it stays static. Now that wearable electronics products move, the printed circuit has to move, the assembly has to move, and a better understanding of the use condition to maintain circuit integrity has to be understood. Printed circuits are primarily copper and polymer systems, the dielectric—what materials are chosen is based on what the requirements are of the end product. In my group we understand the end-product so we can engineer and

### THE CHALLENGES OF THE FAST-MOVING WEARABLES MARKET continues

select those materials best suited for a reliable, wearable product.

Matties: You've mentioned that electronics can learn from other industries—like apparel for instance?

**Vrtis:** Apparel is one. From an electronics standpoint, we're getting smarter in that area. How do we integrate our electronics into that fabric system? Do you use the fabric as your substrate, base system and print directly on the fabric, or place it in the fabric? Printed electronics is going to be very important in the apparel side, where there are multiple circuit pattern application options such as stencil print, screen print, inkjet, and others. Making the circuit pattern on a fabric is fairly simple, but when you are putting that it into a jacket or some sort of a shirt to wear, how do you link all of the circuits together?

Matties: So if we fast-forward 10 years from now, the level of complexity and functionality has got to be just crazy.

**Vrtis:** Consider what happened with the phones. It's amazing the amount of density that is now in the phones from a printed circuit standpoint. The displays have become so much better and bigger. If you think about a wearable, everything is going to have to be some sort of flexible circuitry, and be able to handle stresses such as flexing; the material side of the business and the equipment side are truly going to enable what can happen. Getting in front of that and positioning with roadmapping activities that predict the trends is essential. Other aspects, of course, are power and recharging requirements. Right now, you can easily plug in a phone, but if you're wearing one of these smart watches or it's a medical device and you want or need it 24/7, how do you recharge? What does the battery look like? What happens when you immerse it water? There are a lot of things that need to converge to make advanced wearable solutions happen. In 10 years, I think the material side, the equipment side, and definitely the vision of people thinking of these things that seem way out of the box are all going to drive some of the new technologies.

Matties: Is there anything else you would like to share about this technology?

**Vrtis:** Yes, probably one more thing. One of the very important things in wearable products is making sure it has sustainability. In the medical sector of the business of Multek and Flextronics, we are seeing very interesting opportunities in wearable technology. Of course, in some cases it has to go through a lot of regulatory steps. What has been learned from the consumer side of business is now transcending into the medical side and that sustainability is going to be critical.

**Matties:** When I think of medical and wearables. I think of extending lives, because of the instant feedback and the potential for notification that something might be happening prior to an event.

**Vrtis:** All these wearables are really part of this intelligence of things, right? You want to connect everything. People talk about big data...what is that data and how can we learn from it? The world is now connected. The formatting of connecting, the data of connecting and then also making sure there is security around that data is really going to be important. Since so many people want to have their phones connected to other things, the phone is definitely the hub, which is how I see it for probably the next few years—until something new comes out. I don't know what that is yet. But the phone will be the hub for anything wearable. When you get into the medical applications, this technology has the opportunity to help so many people because the patient can be at home and the doctor or profession-

### THE CHALLENGES OF THE FAST-MOVING WEARABLES MARKET continues

al can receive information from the patient's wearable system in real time status and make some tweaks, via a phone call, or notify the patient to come in for a visit.

**Matties:** It's an exciting time to be alive. Of course, when the toaster came along that was pretty exciting.

**Vrtis:** That was pretty cool, too! (laughs)

**Matties:** Not that I remember it specifically, but I can imagine, "Look what we can do with our bread!" Okay, moving right along, in terms of Multek and Flextronics, where's the manufacturing taking place?

**Vrtis:** We manufacture globally. Flextronics has more than 200K employees operating in more than 100 locations in 30 countries. Our high-volume manufacturing in Multek takes place in Northfield, Minnesota, and Zhuhai, China. In total, we have an annual capacity of more than 36 million square feet of printed circuits. And we continue to make investments in additional capacity and technologies to grow our business. We support every industry and we're in every industry where printed circuits are needed. We leverage earnings across multiple industry applications to help enable solutions in the wearable market, and we provide printed circuit technology to automotive, aerospace, white goods, infrastructure and mobile communications. So we have a very broad knowledge base to service these markets.

**Matties:** Joan, thank you for sharing your story with us.

**Vrtis:** Thank you. I appreciate the opportunity. PCB

## **Fascinating Quantum** Transport on a Surface

Topological insulators are an exceptional group of materials. Their interior acts as an insulator, but the surface conducts electricity extremely well. Scientists at the Technische Universität München can now measure this for the first time directly, with extremely high temporal resolution and at room temperature. In addition, they succeeded to influence the direction of the surface currents with a polarized laser beam.

About ten years ago, scientists discovered a group of materials called "topological insulators" with unusual properties. The interior acts as an insulator, but the top three nanometers conduct electricity better than average. A group led by Professor Alexander Holleitner has succeeded for the first time, to measure this charge current with picosecond resolution at room temperature. They also made the sensational discovery that they can direct the current by the help of circularly polarized light.